| 3  | Welcome from the Chair                  |  |  |  |  |  |  |  |

|----|-----------------------------------------|--|--|--|--|--|--|--|

| 4  | Acknowledgements                        |  |  |  |  |  |  |  |

| 5  | Governor's Welcome                      |  |  |  |  |  |  |  |

| 6  | What's New at SC13                      |  |  |  |  |  |  |  |

| 7  | General Information                     |  |  |  |  |  |  |  |

|    | 8 Registration and Conference Store     |  |  |  |  |  |  |  |

|    | 8 Exhibit Hall Hours                    |  |  |  |  |  |  |  |

|    | 8 SC13 Information Booth                |  |  |  |  |  |  |  |

|    | 8 SC14 Preview Booth                    |  |  |  |  |  |  |  |

|    | 8 SC 25th Anniversary                   |  |  |  |  |  |  |  |

|    | 8 Social Events                         |  |  |  |  |  |  |  |

|    | 9 Conference Services/Convention Center |  |  |  |  |  |  |  |

|    | Facilities                              |  |  |  |  |  |  |  |

|    | 11 Registration Pass Access             |  |  |  |  |  |  |  |

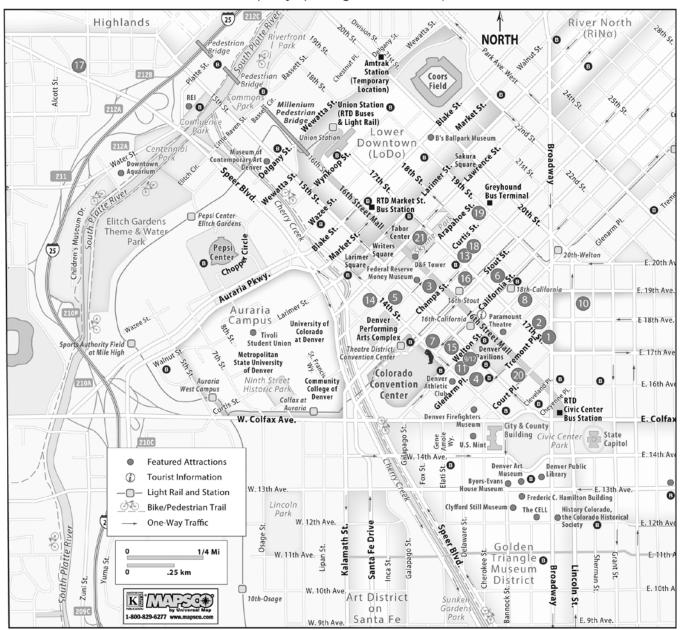

| 13 | Map/Daily Schedules                     |  |  |  |  |  |  |  |

|    | 14 Downtown Area Map                    |  |  |  |  |  |  |  |

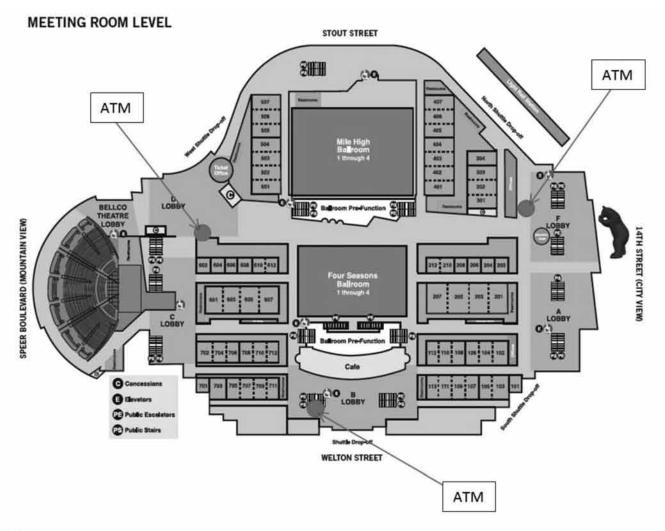

|    | 15 Meeting Room Layout                  |  |  |  |  |  |  |  |

|    | 16 Daily Schedules                      |  |  |  |  |  |  |  |

| 24 | Keynote/Invited Talks/Panels            |  |  |  |  |  |  |  |

|    | 25 Keynote                              |  |  |  |  |  |  |  |

|    | 25 Invited Talks                        |  |  |  |  |  |  |  |

|    | 34 Panels                               |  |  |  |  |  |  |  |

| 36 | Awards                                  |  |  |  |  |  |  |  |

| 40 | Papers                                  |  |  |  |  |  |  |  |

| 64  | Post     | ters/Scientific Visualization     |  |  |  |  |  |  |  |

|-----|----------|-----------------------------------|--|--|--|--|--|--|--|

|     | Showcase |                                   |  |  |  |  |  |  |  |

|     | 65       | Research Posters                  |  |  |  |  |  |  |  |

|     | 83       | ACM Student Research Competition  |  |  |  |  |  |  |  |

|     |          | Posters                           |  |  |  |  |  |  |  |

|     | 88       | Scientific Visualization Showcase |  |  |  |  |  |  |  |

| 93  | Tuto     | orials                            |  |  |  |  |  |  |  |

| 103 | Wor      | kshops                            |  |  |  |  |  |  |  |

| 111 | Bird     | s of a Feather/ACM SIGHPC Meetin  |  |  |  |  |  |  |  |

| 127 | Eme      | erging Technologies               |  |  |  |  |  |  |  |

| 132 |          | ibitor Forum/HPC Impact<br>wcase  |  |  |  |  |  |  |  |

|     | 133      | Exhibitor Forum                   |  |  |  |  |  |  |  |

|     | 142      | HPC Impact Showcase               |  |  |  |  |  |  |  |

|     |          | The impact showcast               |  |  |  |  |  |  |  |

| 147 | HPC      | Interconnections                  |  |  |  |  |  |  |  |

|     | 148      | Broader Engagement/HPC Educators  |  |  |  |  |  |  |  |

|     | 157      | Doctoral Showcase                 |  |  |  |  |  |  |  |

|     | 163      | Student Cluster Competition       |  |  |  |  |  |  |  |

|     | 164      | Experiencing HPC for              |  |  |  |  |  |  |  |

|     |          | Undergraduates                    |  |  |  |  |  |  |  |

| 165 | SCir     |                                   |  |  |  |  |  |  |  |

**Network Research Exhibition**

**SC Silver Anniversary Exhibits**

**SC14 Call for Participation**

166

170

171

Welcome 3

# Welcome to SC13 Bill Gropp, SC13 General Chair

Long-time HPC community members know that SC is the hub of our community. While there are many, many excellent technical conferences in HPC, SC, sponsored each year by the Association for Computing Machinery and the IEEE Computer Society, is the largest and most diverse conference in our community. Recent conferences have brought together more than 10,000

attendees during conference week from all over the world, truly making it the international conference for high performance computing, networking, storage, and analysis.

Each year SC pulls together the most complete cross-section of the technical work currently being pursued in supercomputing — this is reflected in the quality of the technical papers, the depth of the educational and engagement opportunities, and the breadth of technologies and research showcased on the exhibit floor. A quick look at the topics that will be featured this year shows that our tag line, "HPC Everywhere, Everyday" reflects the impact that HPC, and the people that attend SC, have on all aspects of society around the world.

Inside the convention center things will be bustling. We're expecting more than 350 exhibitors spread over nearly 140,000 square feet of exhibit space. With 26 meeting rooms dedicated to the Technical Program, Exhibitor Forum, Tutorials, Workshops, and HPC Interconnections, and two ballrooms for Technical Program events, there'll be plenty of space for all of our events, yet laid out in a way that makes it quick and easy to find your way around.

SC's continuing goal is to provide an informative, high-quality technical program that meets the highest academic standards. The Technical Program is highly competitive and one of the broadest of any HPC conference, with venues ranging from invited talks, panels, and research papers to tutorials, workshops, posters, and Birds-of-a-Feather (BOF) sessions. And this year we are honoring SC's legacy of success by extending peer review to cover every aspect of the technical program. I am also excited by the Emerging Technologies exhibits we have added to the program this year: these are peer-reviewed research projects that will be demonstrated on the show floor. Whether you are unveiling new research for the first time, or helping teach the HPC body of knowledge to the next generation, being part of the SC technical program is a rite of passage in any HPC career.

SC is fundamentally a technical conference, and anyone who has spent time on the show floor knows that the SC Exhibits program provides a unique opportunity to interact with the

future of HPC. Far from being just a simple industry exhibition, our research and industry booths showcase recent developments in our field, with a rich combination of research labs, universities, and other organizations and vendors of all types of software, hardware, and services for HPC.

HPC Interconnections, or "HPCI" for short, is our new name for the SC Communities program. The new name reflects our renewed emphasis on providing an "on ramp" into the excitement that is SC and the field of high performance computing. HPCI is designed to help everyone get more out of the conference than ever, providing programs for everyone interested in building a stronger HPC community, including students, educators, researchers, international attendees and under-represented groups.

One of the defining characteristics of SC is SCinet, the conference network that, for the week of the conference, is one of the largest and most advanced networks in the world. While many attendees experience SCinet directly as wireless networking that is provided throughout the convention center, SCinet also provides a once-a-year opportunity for research and engineering groups to work with some of the most modern networking equipment and very high bandwidth wide area networking. This year, SCinet will exceed 1Terabit/second of networking bandwidth! During the conference please be sure to stop by the SCinet booth for more information on the networking infrastructure, and check out the SCinet research exposition presentations on Thursday to witness firsthand the future of high performance networks.

This year the conference will mark its 25th anniversary. in recognition of our silver anniversary, and of the lasting contribution that our participants have made to the HPC state of the art, we are hosting several new activities that look back on the progress in our field as seen through the lens of SC. There are exhibits of technology—many of which were first described or seen at SC—on the exhibit floor. A panel will talk about what we've learned over the years, and how that can help us as we confront the coming end of Moore's law and the changes in software, algorithms, and hardware that will be required in the coming decade. Also new this year is a new award for the most influential paper presented at SC that has stood the test of time in our "Test of Time" award.

# Welcome to Denver!

For a quarter of a century, the Supercomputing Conference has served as the crossroads for the entire HPC community. Denver is a community at the crossroads of the country, located near the center of the continental United States, at the convergence of mountain and prairie, where high-rise buildings greet open range and the earth touches the sky. I can't think of a better place to celebrate SC's rich past, and our community's bright future. Welcome to Denver and to SC13!

4 Acknowledgements

# Acknowledgements

No conference this size could be possible without the dedication, commitment and passion of the SC13 committee. The core committee includes more than 100 people who have largely volunteered their time planning for this event for more than three years. Added to that number are the more than 500 people who have helped review submissions and contributed to the planning and preparations. The full list of committee members is posted on the conference website at sc13.supercomputing.org.

### **SC13 Committee Management**

### **Conference Chair**

**William Douglas Gropp**, University of Illinois at Urbana-Champaign

### **Deputy General Chair**

Trish Damkroger, Lawrence Livermore National Laboratory

### **Executive Committee Vice Chair**

**Scott Lathrop**, Shodor/National Center for Supercomputing Applications

### **Executive Assistant**

**Beth McKown**, National Center for Supercomputing Applications

Carolyn Peters, Argonne National Laboratory

### **Future Chair**

Jackie Kern, University of Illinois at Urbana-Champaign

# **Society Reps - ACM**

Donna Cappo, ACM Ashley Cozzi, ACM

### Society Reps - IEEE/CS

**Brookes Little**, IEEE Computer Society **Carmen Saliba**, CMP, IEEE Computer Society

### **Communications Chair**

John West, DOD HPC Modernization Program

### **Exhibits Chair**

Jim Costa, Sandia National Laboratories

### **Finance Chair**

Becky Verastegui, Oak Ridge National Laboratory

### **HPC Interconnections Chair**

Elizabeth Jessup, University of Colorado Boulder

### **Infrastructure Chairs**

**Christine E. Cuicchi**, HPC Modernization Program **Tim Yeager**, US Air Force Research Laboratory

### **SCinet Chair**

Trey Breckenridge, Mississippi State University

# **Silver Anniversary Chair**

Mary Hall, University of Utah

# **Technical Program Chair**

Satoshi Matsuoka, Tokyo Institute of Technology

# STATE OF COLORADO

# **EXECUTIVE CHAMBERS**

136 State Capitol Denver, CO 80203 - 1792 Phone (303) 866-2471

November 17, 2013

# Greetings:

On behalf of the State of Colorado, it is my pleasure to welcome you to SC13, the International Conference for High Performance Computing (HPC), Networking, Storage, and Analysis. This year we are proud to be hosting this prestigious event at the Colorado Convention Center in downtown Denver, Colorado.

Attracting thousands of research and technology leaders from around the world, this conference represents a remarkable opportunity to meet new collaborators and experience the historic innovation that is changing the landscape of this industry.

We invite you to enjoy the beauty that is Colorado – from our majestic mountains and wide-open plains to our bustling cities and invigorating climate. In addition to our natural beauty, Colorado has also emerged as a hotspot for start-ups, entrepreneurship, business and innovation, and I hope you experience the energy and collaborative spirit of our welcoming state.

Best wishes for a successful conference, and we look forward to your return visit.

Sincerely,

Jøhn W. Hickenlooper

Governor

6 What's New at SC13

# What's New at SC13

In addition to the programs you've come to expect at SC, you'll find these new opportunities to learn more about all things HPC:

- Emerging technologies, a peer-reviewed addition to the technical program that showcases new developments; you'll find this on the exhibit floor.

- HPC Impact Showcase highlights the use of HPC, from consumer goods to industrial applications. Also on the exhibit floor—come see how HPC is changing the world.

- Test of Time Award is for the paper, presented at SC, that has had the greatest sustained impact on our field. Presented on Thursday, along with the first ever ACM Athena Lecture at SC.

- HPC Interconnections is our new name for the SC Communities program, to emphasize the focus on providing an "on ramp" into the excitement of our field. New this year is a closer integration with the technical program. Have a look at the offerings of the HPC Educator and Broader Engagement programs; the sessions beginning Tuesday are open to all Technical Program attendees.

- In celebration of the 25th anniversary of SC we have special exhibits, including some at participating exhibitors, and a panel discussing the past and future of our field.

In this section, you'll find information on registration, exhibit hours, conference store hours, descriptions and locations of all conference social events, information booths and their locations, as well as convention center facilities and services.

# General Information

# **General Information**

# **Registration and Conference Store**

The registration area and conference store are located on the 1st floor of the Denver Convention Center Lobby area.

### Hours:

| Saturday, November 16  | 1pm – 6pm    |

|------------------------|--------------|

| Sunday, November 17    | 7am – 6pm    |

| Monday, November 18    | 7am – 9pm    |

| Tuesday, November 19   | 7:30am – 6pm |

| Wednesday, November 20 | 7:30am – 6pm |

| Thursday, November 21  | 7:30am – 5pm |

| Friday, November 22    | 8am – 11am   |

|                        |              |

# **Registration Pass Access**

See page 11 for access grids.

### **Exhibit Hall Hours**

| Tuesday, November 19   | 10am-6pm |

|------------------------|----------|

| Wednesday, November 20 | 10am-6pm |

| Thursday, November 21  | 10am-3pm |

# **Age Requirements Policy**

- Technical Program attendees must be 16 years of age or older. Age verification is required.

- Exhibits-Only registration is available for children ages 12-16. Age verification is required.

- Children 12 and under are not permitted in the Exhibit Hall other than on Family Day (see page 13 details).

- Children under 16 are not allowed in the Exhibit Hall during installation, dismantling or before or after posted exhibit hours. Anyone under 16 must be accompanied by an adult at all times while visiting the exhibition.

### **SC13 Information Booth**

Need up-to-the-minute information about what's happening at the conference. Need to know where to find your next session? What restaurants are close by? Where to get a document printed? These questions and more can be answered by a quick stop at one of the SC Information booths. There are two booth locations for your convenience: one is in F Lobby, near the Blue Bear entrance, next to the conference store; the second booth is located in the open area near the Mile High ballroom and 600 series rooms.

### Information Booth hours are:

| Saturday, November 16  | 1pm-6pm                                                           |

|------------------------|-------------------------------------------------------------------|

| Sunday, November 17    | 7am-6pm                                                           |

| Monday, November 18    | 7am-9pm                                                           |

| Tuesday, November 19   | 7:30am-6pm                                                        |

| Wednesday, November 20 | 7:30am-6pm                                                        |

| Thursday, November 21  | 7:30am-5pm                                                        |

| Friday, November 22    | <b>8am-11pm</b> (the booth near the Mile High ballroom is closed) |

### **SC14 Preview Booth**

Members of next year's SC committee will be available in the SC14 preview booth (located in A Lobby - across from Registration) to offer information and discuss next year's SC conference in New Orleans. Stop by for a copy of next year's Call for Participation and pick up some free gifts!

The booth will be open during the following hours:

| Tuesday, November 19   | 10am-4pm |

|------------------------|----------|

| Wednesday, November 20 | 10am-4pm |

| Thursday, November 21  | 10am-4pm |

### **SC 25th Anniversary**

SC13 plans several activities in celebration of the Silver Anniversary of the conference. The signature event will be a panel on Thursday afternoon titled "Retrospective on Supercomputing Technologies." In addition, there will be special exhibits, historical displays and recognition of attendees and exhibitors who have participated in all 25 SC conferences.

### **Social Events**

# **Exhibitors' Party (Coors Field)**

Sunday, November 17 6pm-9pm

Take me out to the ball park! SC13 is hosting an Exhibitors' Party for registered exhibitors. The party is SC13's way of thanking exhibitors for their participation and support of the conference. The party will be held at Coors Field, home of The Colorado Rockies professional baseball team. Everyone is encouraged to wear the jersey of their favorite sports team. The party will feature a live (and lively!) band, self-guided tours of the facility, including the visitor's locker room and dug out, games, and ballpark food and drinks throughout the facility.

Transportation is provided from B Lobby of the convention center to Coors Field starting at 5:45pm.

An Exhibitor badge, party ticket, and government-issued photo ID are required to attend this event.

# **Exhibits Gala Opening Reception (Exhibit Hall)**

# Monday, November 18 7pm-9pm

SC13 will host its annual Grand Opening Gala in the Exhibit Hall. This will be your first opportunity to see the latest high performance computing, networking, storage, analysis, and research products, services, and innovations. This event is open to all Technical Program, Exhibitors and HPC Interconnections Program (Broader Engagement, HPC Educators and Student Volunteers) registrants.

# Posters Reception (Mile High Pre-Function Area) Tuesday, November 19 5:15pm-7pm

The reception is an opportunity for attendees to interact with poster presenters and includes research, electronic, and the ACM Student Research Competition (SRC) posters. The reception is open to all attendees with Technical Program registration. Complimentary refreshments and appetizers are available until 7pm.

# **Scientific Visualization Showcase Reception**

(Mile High Pre-Function Area) Tuesday, November 19 5:15pm-7pm

After you have viewed the posters at the Posters Reception, stop by the Scientific Visualization Showcase Reception. The reception is open to all attendees with Technical Program registration. The reception is located in the Mile High Ballroom Pre-function area.

# **Technical Program Conference Reception**

(Denver Museum of Nature & Science) Thursday, November 21 7pm-10pm Buses Leave from B Lobby

SC13 is hosting a conference reception for all Technical Program attendees. Join us for delicious food, beverages, and entertainment at Denver Museum of Nature and Science (www.dmns.org). The Denver Museum of Nature & Science is the Rocky Mountain region's leading resource for informal science education. A variety of exhibitions and activities will be available for attendees to experience the natural wonders of Colorado, Earth, and the Universe.

A Technical Program badge, event ticket, and government-issued photo ID are required to attend this event. Attendees are required to wear technical program badges throughout the reception, and badges may be checked during the event.

Shuttle transportation to and from the event will run 6:30pm-10pm from B Lobby of the convention center (look for buses with "DMNS" signs in the front window).

# **ACM SIGHPC Annual Members Meeting** See page 114.

# Conference Services/Convention Center Facilities

### **SC13 Mobile App**

Go Mobile with Boopsie—the SC13 App

Access the SC13 schedule, session and paper abstracts, information on speakers, exhibit maps, local information and more with your smart phone! Just go to your phone's app store and download the free SC13 app from Boopsie. You can access the SC13 app in one of two ways:

- 1. Direct from Boopsie (sc13.boopsie.com) from your smart phone.

- Go to the App Store on your smart phone and search for 'SC13'.

The SC13 Boopsie app provides a searchable conference schedule, including session type, speaker(s), location, time and duration. It includes a complete roster of speakers, cross-correlated with the sessions in which they will appear. If you're looking for "What's Next" at SC13, there's even a handy feature to alert you to sessions starting in the next 60 minutes. Need to find a vendor's booth? There's a complete Exhibitor listing with booth numbers and a map of the exhibit floor. Included in the app are conference-related social media information including a direct link to the conference Facebook page and Twitter feeds, so you can see what is hot at the conference without needing to leave the app to check your phone's Twitter app.

### **ATMs**

Three ATMs are located within the convention center: F Lobby, B Lobby and D Lobby.

### **Attendee Lounge**

Need to take a minute to relax before your next session? The attendee lounge is the place to do that. It is located in B Lobby, Sunday, November 17 through Friday, November 22 from 8:30am – 5pm.

# **Business Center**

The Business Center is located off A Lobby in the red carpeted concourse of the convention center. The center is open 7:30am-5:30pm during convention days. For more information please contact: bborgerding@myofficeco.com or call 720.904.2300.

# **City and Dining Information**

The information kiosk is located in the F Atrium, near the Blue Bear. It is staffed by Visit Denver.

# Coat & Bag Check

The coat and bag check station is located in A Lobby. The hours are as follows:

| Saturday, November 16  | 7am-5:30pm     |

|------------------------|----------------|

| Sunday, November 17    | 7:00am-6pm     |

| Monday, November 18    | 7:30am -9:30pm |

| Tuesday, November 19   | 7:30am-7:30pm  |

| Wednesday, November 20 | 7:30am-7:30pm  |

| Thursday, November 21  | 7:30pm-7:30pm  |

| Friday, November 22    | 7:30pm-3:30pm  |

### **Emergency Contact**

For an onsite emergency, please call 303.228.8030 or dial 200 on a beige house phone.

# **Family Day**

Family Day is Wednesday, November 20, 4pm-6pm. Adults and children 12 and over are permitted on the floor during these hours when accompanied by a registered conference attendee.

# **First-Aid Center**

The first-aid center is located in E Lobby near room 507.

# **Lost Badge**

There is a \$40 processing fee to replace a lost badge. Lost and found is located at the Coat Check station, A Lobby.

# **Parking**

The Colorado Convention Center offers 1,000 on-site parking spaces with direct access to the center and the Denver Performing Arts Complex. It is open 24/7 to all visitors attending any event or business in the downtown area. For more information, see the website at: denverconvention.com/attend-an-event/parking.

# **Prayer & Meditation Room**

The prayer and meditation room is located in Room 602 of the convention center. It is open 9am-6pm, Sunday, November 17 through Friday, November 22.

### **Restrooms**

Restrooms are located conveniently throughout the convention center. See page 15 for locations.

# Wheelchair/Scooter Rental

Wheelchairs and medical mobility scooters are available for rent at the Business Center. Wheelchairs are \$4/hour or \$15/day; scooters are \$10/hour or \$40/day.

# **Registration Pass Access**

# **Registration Pass Access - Technical Program**

Each registration category provides access to a different set of conference activities, as summarized below.

| Type of Event                                    | Tutorials | Technical<br>Program | Technical<br>Program<br>+ Workshops | Workshop<br>Only |

|--------------------------------------------------|-----------|----------------------|-------------------------------------|------------------|

| Awards (Thursday)                                |           | *                    | *                                   | *                |

| Birds-of-a-Feather                               |           | *                    | *                                   |                  |

| Broader Engagement & Educator Sessions (Sun/Mon) |           |                      | *                                   | *                |

| Broader Engagement &                             |           |                      |                                     |                  |

| Educator Sessions (Tue-Thu)                      |           | *                    | *                                   |                  |

| Conference Reception (Thursday)                  |           | *                    | *                                   |                  |

| Exhibit Floor                                    |           | *                    | *                                   |                  |

| Exhibitor Forum                                  |           | *                    | *                                   |                  |

| Exhibits Gala Opening (Monday)                   |           | *                    | *                                   |                  |

| Invited Talks (Non-Plenary)                      |           | *                    | *                                   |                  |

| Invited Talks (Plenary)                          |           | *                    | *                                   |                  |

| Keynote (Tuesday)                                |           | *                    | *                                   |                  |

| Panels (Tue-Thur)                                |           | *                    | *                                   |                  |

| Panels (Friday Only)                             |           | *                    | *                                   |                  |

| Papers                                           |           | *                    | *                                   |                  |

| Posters                                          |           | *                    | *                                   |                  |

| Poster Reception (Tuesday)                       |           | *                    | *                                   |                  |

| Tutorial Lunch (Sun/Mon ONLY)                    | *         |                      |                                     |                  |

| Tutorial Sessions                                | *         |                      |                                     |                  |

| Student Cluster Competition                      |           | *                    | *                                   |                  |

| Workshops                                        |           |                      | *                                   | *                |

# **Registration Pass Access**

# **Registration Pass Access - Exhibits**

Each registration category provides access to a different set of conference summarized below.

| Type of Event                  | Exhibitor | Exhibit<br>Hall<br>Only |

|--------------------------------|-----------|-------------------------|

| Awards (Thursday)              | *         | *                       |

| Birds-of-a-Feather             | *         |                         |

| Exhibit Floor                  | *         | *                       |

| Exhibitor Forum                | *         |                         |

| Exhibits Gala Opening (Monday) | *         |                         |

| Exhibitor's Reception          | *         |                         |

| Invited Talks (Plenary)        | *         |                         |

| Keynote (Tuesday)              | *         |                         |

| Panels (Friday Only)           | *         |                         |

| Posters                        | *         | *                       |

| Student Cluster Competition    | *         |                         |

# **Registration Pass Access - Press**

Each registration category provides access to a different set of conference summarized below.

| Type of Event                     | Press |  |

|-----------------------------------|-------|--|

|                                   |       |  |

| Awards (Thursday)                 | *     |  |

| Birds-of-a-Feather                | *     |  |

| Broader Engagement & Educator     |       |  |

| Sessions (Sun/Mon)                | *     |  |

| Broader Engagement & Educator     |       |  |

| Sessions (Tue-Thu)                | *     |  |

| Conference Reception (Thursday)   | *     |  |

| Exhibit Floor (during show hours) | *     |  |

| Exhibitor Forum                   | *     |  |

| Exhibits Gala Opening (Monday)    | *     |  |

| Invited Talks (Non-Plenary)       | *     |  |

| Invited Talks (Plenary)           | *     |  |

| Keynote (Tuesday)                 | *     |  |

# **Maps/Daily Schedules**

A schedule of each day's activities—by time/event/location—

is provided in this section, along with a map of the Downtown area

and meeting rooms.

# In the second of the second of

# SC 2013 Hotel Map Denver, CO November 17-22, 2013

| Н | otel Distance                         | ce to CCC | Но | tel                             | Distanc | e to CCC  | Hot | el Distanc                     | ce to CCC |

|---|---------------------------------------|-----------|----|---------------------------------|---------|-----------|-----|--------------------------------|-----------|

| 1 | The Brown Palace Hotel & Spa          | 5 Blocks  | 8  | Grand Hyatt Denver              |         | 3 Blocks  | 16  | Magnolia Hotel                 | 3 Blocks  |

| 2 | Comfort Inn Downtown                  | 5 Blocks  | 9  | Hampton Inn & Suites Denver @ C | CCC     | 1 Block   | 17  | Residence Inn Downtown Denver  | 1.5 Miles |

| 3 | Courtyard by Marriott Denver Downtown | 3 Blocks  | 10 | Hampton Inn & Suites Downtown   |         | 0.9 Miles | 18  | Residence Inn by Marriott      | 5 Blocks  |

| 4 | Crowne Plaza                          | 2 Blocks  | 11 | Hilton Garden Inn Downtown Denv | ver     | 1 Block   |     | Denver City Center             |           |

| 5 | Curtis, a Doubletree Hotel            | 2 Blocks  | 12 | Homewood Suites Denver Downto   | own     | 1 Block   | 19  | Ritz-Carlton Denver            | 7 Blocks  |

| 6 | Denver Marriott City Center           | 4 Blocks  | 13 | Hotel Monaco Denver             |         | 4 Blocks  | 20  | Sheraton Denver Downtown Hotel | 3 Blocks  |

| 7 | Embassy Suites Denver Downtown @ CCC  | 50 Steps  | 14 | Hotel Teatro                    |         | 3 Blocks  | 21  | Westin Denver Downtown         | 5 Blocks  |

|   |                                       |           | 15 | Hyatt Regency Denver @ CCC      |         | 50 Steps  |     |                                |           |

# **ATMs**

Three ATMs are located within the convention center, and you can find these located in the F Lobby, B Lobby and the D Lobby as shown above.

# Restrooms

Restrooms are located conveniently throughout the convention center, as follows:

| Exhibit Halls:      | Street Level (refer to map above, high- | Ballrooms:         |  |

|---------------------|-----------------------------------------|--------------------|--|

| Hall A south & east | lighted in blue):                       | Pre-function space |  |

| Hall B south        | A, C, D, Lobby                          | Bellco Theatre:    |  |

| Hall C south & west | B Lobby east & west                     | Lobby & Corridor   |  |

| Hall D west & north | 300, 400, 500 Corridor                  |                    |  |

| Hall E north        | F Lobby                                 |                    |  |

| Hall F north        |                                         |                    |  |

# Saturday, November 16

| rime      | Event              | Session          | Location        |

|-----------|--------------------|------------------|-----------------|

| Noon-4:30 | HPC Educators      | LittleFe Setup   | 702/704/706     |

| 1:00-5:30 | HPC Educators      | Registration     | 708/710/712     |

| 1:30-5:00 | Broader Engagement | Registration     | 705/707/709/711 |

| 5:00-6:00 | Broader Engagement | Orientation      | 705/707/709/711 |

| 6:00-7:00 | HPC Educators      | Orientation      | 705/707/709/711 |

| 7:00-9:00 | BE/HPC Educators   | Networking Event | B Lobby         |

|           |                    |                  |                 |

# Sunday, November 17

| Time       | Event              | Session                                                                | Location        |

|------------|--------------------|------------------------------------------------------------------------|-----------------|

| 8:30-10:00 | BE/HPC Educators   | Plenary I: Making Parallelism Easy: A 25-Year Odyssey                  | 705/707/709/711 |

| 8:30-Noon  | Tutorial           | Hybrid MPI and OpenMP Parallel Programming                             | 407             |

| 8:30-Noon  | Tutorial           | InfiniBand/High-speed Ethernet for Dummies                             | 201/203         |

| 8:30-Noon  | Tutorial           | A "Hands-on" Large Scale Visualization with ParaView                   | 405             |

| 8:30-5:00  | Tutorial           | Introduction to OpenMP                                                 | 402             |

| 8:30-5:00  | Tutorial           | Advanced MPI Programming                                               | 406             |

| 8:30-5:00  | Tutorial           | Debugging MPI & Hybrid/Heterogeneous Applications at Scale             | 404             |

| 8:30-5:00  | Tutorial           | Globus Online and the Science DMV                                      | 403             |

| 8:30-5:00  | Tutorial           | Hands-on Practical Hybrid Parallel Application Performance Engineering | 301             |

| 8:30-5:00  | Tutorial           | OpenACC: Productive, Portable Performance on Hybrid Systems            | 401             |

| 8:30-5:00  | Tutorial           | Parallel Computing 101                                                 | 303             |

| 8:30-5:00  | Tutorial           | Programming for the Intel Xeon Phi                                     | 205/207         |

| 8:30-5:00  | Tutorial           | Structured Parallel Programming with Patterns                          | 302             |

| 9:00-5:30  | Workshop           | 1st Workshop on Sustainable Software for Science                       | 503             |

| 9:00-5:30  | Workshop           | 4th Workshop on Petascale (Big) Data Analytics                         | 501             |

| 9:00-5:30  | Workshop           | 6th Workshop on Many-Task Computing on Clouds, Grids                   | 502             |

| 9:00-5:30  | Workshop           | Building Energy Efficient HPC                                          | 603             |

| 9:00-5:30  | Workshop           | IA^3 2013 - 3rd Workshop on Irregular Applications, Architectures      | 504             |

| 9:00-5:30  | Workshop           | 3rd Intl Workshop on Network-Aware Data Management                     | 601             |

| 9:00-5:30  | Workshop           | 4th Intl Workshop on Data-Intensive Computing in the Clouds            | 507             |

| 9:00-5:30  | Workshop           | 8th Workshop on Ultrascale Visualization                               | 505             |

| 9:00-5:30  | Workshop           | 8th Workshop on Workflows in Support of                                | 506             |

| 10:30-Noon | Broader Engagement | Fortran 2008 Coarrays and Performance Analysis                         | 705/707/709/711 |

| 10:30-Noon | HPC Educators      | Supercomputing in Plain English                                        | 708/710/712     |

| 10:30-5:00 | HPC Educators      | LittleFe Buildout                                                      | 702/704/706     |

| 1:30-3:00  | Broader Engagement | Hands-on Exercise: Performance Analysis with TAU                       | 705/707/709/711 |

| 1:30-5:00  | HPC Educators      | Curriculum Workshop: Mapping CS2013 & NSF/TCPP                         | 708/710/712     |

| 1:30-5:00  | Tutorial           | Advanced Topics in InfiniBand/High-Speed Ethernet for Designing Hi-End | 201/203         |

| 1:30-5:00  | Tutorial           | Practical Fault Tolerance on Today's HPC Systems                       | 405             |

| 1:30-5:00  | Tutorial           | Scaling I/O Beyond 100,000 Cores using ADIOS                           | 407             |

# **Sunday, November 17** (Continued)

| Time      | Event              | Session                                 | Location                  |

|-----------|--------------------|-----------------------------------------|---------------------------|

| 3:30-5:00 | Broader Engagement | Graphics and Visualization Technologies | 705/707/709/711           |

| 6:00-9:00 | Social Event       | Exhibitors' Party                       | Buses depart from B Lobby |

# Monday, November 18

| Time       | Event              | Session                                                                                | Location                          |

|------------|--------------------|----------------------------------------------------------------------------------------|-----------------------------------|

| 8:30-10:00 | BE/HPC Educators   | Plenary Talk II                                                                        | 705/707/709/711                   |

| 8:30-Noon  | Tutorial           | Advanced PGAS Programming in UPC                                                       | 303                               |

| 8:30-Noon  | Tutorial           | Effective Procurement of Supercomputers                                                | 302                               |

| 8:30-Noon  | Tutorial           | How to Analyze the Performance of Parallel Codes 101                                   | 301                               |

| 8:30-5:00  | Tutorial           | Advanced OpenMP: Performance and 4.0 Features                                          | 406                               |

| 8:30-5:00  | Tutorial           | Asynchronous Hybrid and Heterogeneous Parallel Programming with MPI/OmpSs              | 401                               |

| 8:30-5:00  | Tutorial           | Debugging and Optimizing MPI and OpenMP Applications Running on CUDA                   | 405                               |

| 8:30-5:00  | Tutorial           | Ensuring Network Performance with perfSONAR                                            | 402                               |

| 8:30-5:00  | Tutorial           | Linear Algebra Libraries for HPC: Scientific Computing with Multicore and Accelerators | 407                               |

| 8:30-5:00  | Tutorial           | OpenCL: A Hands-On Introduction                                                        | 403                               |

| 8:30-5:00  | Tutorial           | Parallel I/O in Practice                                                               | 205/207                           |

| 8:30-5:00  | Tutorial           | Python in HPC                                                                          | 201/203                           |

| 8:30-5:00  | Tutorial           | The Practitioner's Cookbook for Good Parallel Performance on Multi- and                | 404                               |

| 9:00-Noon  | Workshop           | "Building" Energy Efficient High Performance Computing: 4th Annual EE HPC WG           | 603                               |

| 9:00-5:30  | Workshop           | 4th Intl Workshop on Performance Modeling, Benchmarking and Simulation of              | 502                               |

| 9:00-5:30  | Workshop           | 4th Workshop on Latest Advances in Scalable Algorithms for Large-Scale Systems (ScalA) | 507                               |

| 9:00-5:30  | Workshop           | Energy Efficient SuperComputing (E2SC)                                                 | 210/120 (morning) 603 (afternoon) |

| 9:00-5:30  | Workshop           | Extreme-Scale Programming Tools                                                        | 501                               |

| 9:00-5:30  | Workshop           | Python for High Performance and Scientific Computing (PyHPC 2013)                      | 505                               |

| 9:00-5:30  | Workshop           | The 6th Workshop on HPC Finance                                                        | 601                               |

| 9:00-5:30  | Workshop           | The 8th Parallel Data Storage Workshop                                                 | 503                               |

| 9:00-5:30  | Workshop           | WOLFHPC: Workshop on Domain-Specific Languages and High-Level Frameworks for HPC       | 506                               |

| 9:00-6:00  | Workshop           | The 2nd International Workshop on Data Intensive Scalable Computing Systems (DISCS)    | 504                               |

| 10:30-Noon | Broader Engagement | HPC Applications                                                                       | 705/707/709/711                   |

| 10:30-5:00 | HPC Educators      | Workshop on Parallel, Distributed, and HPC in Undergraduate Curricula                  | 708/710/712                       |

| 10:30-5:00 | HPC Educators      | LittleFe Buildout                                                                      | 702/704/706                       |

| 1:30-3:00  | Broader Engagement | Session V: Mentor/Protege Session & Mixer                                              | 705/707/709/711                   |

# Monday, November 18 (Continued)

| Time      | Event                       | Session                                                   | Location               |

|-----------|-----------------------------|-----------------------------------------------------------|------------------------|

| 1:30-5:00 | Tutorial                    | An Overview of Fault-Tolerant Techniques for HPC          | 301                    |

| 1:30-5:00 | Tutorial                    | Effective HPC Visualization and Data Analysis using VisIt | 303                    |

| 1:30-5:00 | Tutorial                    | Introducing R: from Your Laptop to HPC and Big Data       | 302                    |

| 3:00-5:00 | HPC Undergraduate           | Experiencing HPC For Undergraduates Orientation           | 703                    |

| 3:30-5:00 | BE/Student Volunteers       | Professional Development I: Navigating a Computing Career | 705/707/709/711        |

| 6:00-6:30 | HPC Interconnections        | SC First-Timers Introduction                              | 705/707/709/711        |

| 6:00-9:00 | Emerging Technologies       | Emerging Technologies                                     | Booth 3547             |

| 6:00-9:00 | Scientific Viz Showcase     | Exhibit                                                   | Mile High Pre-Function |

| 7:00-8:00 | HPC Impact Showcase         | HPC Impact Showcase Monday                                | Booth 3947             |

| 7:00-9:00 | Student Cluster Competition | Kickoff                                                   | Booth 3146             |

|           |                             |                                                           |                        |

# **Tuesday, November 19**

| Time       | Event                       | Session                                                                            | Location               |

|------------|-----------------------------|------------------------------------------------------------------------------------|------------------------|

| 8:30-10:00 | Keynote                     | The Secret Life of Data (Genevieve Bell)                                           | Mile High              |

| 8:30-5:00  | Posters                     | ACM Student Research Competition Posters                                           | Mile High Pre-Function |

| 8:30-5:00  | Posters                     | Research Posters                                                                   | Mile High Pre-Function |

| 8:30-5:00  | Scientific Viz Showcase     | Exhibit                                                                            | Mile High Pre-Function |

| 10:00-5:30 | Emerging Technologies       | Emerging Technologies                                                              | Booth 3547             |

| 10:00-6:00 | Student Cluster Competition | Student Cluster Competition                                                        | Booth 3146             |

| 10:20-2:30 | HPC Impact Showcase         | Showcase Tuesday                                                                   | Booth 3947             |

| 10:30-Noon | Awards                      | ACM Gordon Bell Finalists I                                                        | 201/203                |

| 10:30-Noon | Papers                      | Data Management in the Cloud                                                       | 205/207                |

| 10:30-Noon | Papers                      | Graph Partitioning and Data Clustering                                             | 401/402/403            |

| 10:30-Noon | Papers                      | Inter-Node Communication                                                           | 405/406/407            |

| 10:30-Noon | BE/Student Volunteers       | Professional Development II: Building Your Technical Resume                        | 601/603                |

| 10:30-Noon | Exhibitor Forum             | Hardware & Architecture I                                                          | 501/502                |

| 10:30-Noon | Exhibitor Forum             | Moving, Managing & Storing Data I                                                  | 503/504                |

| 10:30-Noon | HPC Educators               | Special Session on Education and Workforce Development                             | 708/710/712            |

| 10:30-5:00 | HPC Educators               | LittleFe Buildout                                                                  | 702/704/706            |

| 10:30-Noon | HPC Undergraduate           | Introduction to HPC Research Topics                                                | 703                    |

| 10:30-Noon | Invited Talks               | Invited Talks (1)                                                                  | Mile High              |

| 12:15-1:15 | SIGHPC Meeting              | ACM SIGHPC Annual Members Meeting                                                  | 605                    |

| 12:15-1:15 | Birds of a Feather          | Best Practices for Commissioning Liquid Cooling Infrastructure                     | 404                    |

| 12:15-1:15 | Birds of a Feather          | Building on the European Exascale Approach                                         | 210/212                |

| 12:15-1:15 | Birds of a Feather          | Collaborative Opportunities with the Open Science Data Cloud                       | 205/207                |

| 12:15-1:15 | Birds of a Feather          | Getting Scientific Software Installed: Tools and Best Practices                    | 708/710/712            |

| 12:15-1:15 | Birds of a Feather          | Hadoop 2 and HPC: Beyond MapReduce                                                 | 507                    |

| 12:15-1:15 | Birds of a Feather          | Integration of NVM Technologies in HPC Architectures: Challenges and Opportunities | 601/603                |

| 12:15-1:15 | Birds of a Feather          | Maximize Data Center Power Efficiency through Energy Aware Computing               | 201/203                |

| 12:15-1:15 | Birds of a Feather          | Open MPI State of the Union                                                        | 301/302/303            |

|            |                             |                                                                                    |                        |

# **Tuesday, November 19** (Continued)

|            | ,, 20 (3                |                                                                                     |                        |

|------------|-------------------------|-------------------------------------------------------------------------------------|------------------------|

| Time       | Event                   | Session                                                                             | Location               |

| 12:15-1:15 | Birds of a Feather      | Python for High Performance and Scientific Computing                                | 401/402/403            |

| 12:15-1:15 | Birds of a Feather      | Scalable Adaptive Graphics Environment (SAGE) for Global Collaboration              | 501/502                |

| 12:15-1:15 | Birds of a Feather      | Seventh Graph500 List                                                               | 705/707/709/711        |

| 12:15-1:15 | Birds of a Feather      | The Lustre Community: At the Intersection of HPC and Big Data                       | 405/406/407            |

| 12:15-1:15 | Birds of a Feather      | The Role of Software-Defined Networking in the Big Data Equation                    | 703                    |

| 12:15-1:15 | Birds of a Feather      | TORQUE: Where Are We Now and Where Are We Going                                     | 503/504                |

| 1:30-3:00  | Awards                  | Cray/Fernbach/Kennedy Award Recipients Talks                                        | Mile High              |

| 1:30-3:00  | Invited Talks           | Invited Talks (2)                                                                   | Mile High              |

| 1:30-3:00  | Panel                   | Future of Memory Technology for Exascale and Beyond                                 | 301/302/303            |

| 1:30-3:00  | Papers                  | Cloud Resource Management and Scheduling                                            | 205/207                |

| 1:30-3:00  | Papers                  | Energy Management                                                                   | 401/402/403            |

| 1:30-3:00  | Papers                  | Extreme-Scale Applications                                                          | 201/203                |

| 1:30-3:00  | Papers                  | Load Balancing                                                                      | 405/406/407            |

| 1:30-5:00  | HPC Educators           | Serious Computational Examples for Science Classes Featuring Python, Mathematica    | 705/707/709/711        |

| 1:30-5:00  | HPC Educators           | Strategies for Introducing Parallelism with Python                                  | 708/710/712            |

| 3:30-5:00  | BE/Student Volunteers   | SV Professional Development III: HPC Careers and Networking Panel                   | 601/603                |

| 3:30-5:00  | Exhibitor Forum         | Hardware & Architecture II                                                          | 501/502                |

| 3:30-5:00  | Exhibitor Forum         | Moving, Managing & Storing Data II                                                  | 503/504                |

| 3:30-5:00  | Invited Talks           | Invited Talks (3)                                                                   | Mile High              |

| 3:30-5:00  | Panel                   | Exascale Runtime Systems                                                            | 301/302/303            |

| 3:30-5:00  | Papers                  | Fault Tolerance and Migration in the Cloud                                          | 205/207                |

| 3:30-5:00  | Papers                  | I/O Tuning                                                                          | 405/406/407            |

| 3:30-5:00  | Papers                  | Physical Frontiers                                                                  | 201/203                |

| 3:30-5:00  | Papers                  | System-wide Application Performance Assessments                                     | 401/402/403            |

| 5:15-7:00  | Posters                 | ACM Student Research Competition Poster Reception                                   | Mile High Pre-Function |

| 5:15-7:00  | Posters                 | Research Poster Reception                                                           | Mile High Pre-Function |

| 5:15-7:00  | Scientific Viz Showcase | Reception                                                                           | Mile High Pre-Function |

| 5:30-7:00  | Birds of a Feather      | Asynchronous and Adaptive Parallel Programming with Charm++                         | 702/704/706            |

| 5:30-7:00  | Birds of a Feather      | Campus Bridging with XSEDE and Globus Online                                        | 601/603                |

| 5:30-7:00  | Birds of a Feather      | Defining BigData: Industry Views on Real-Time Data, Analytics, and HPC Technologies | 405/406/407            |

| 5:30-7:00  | Birds of a Feather      | Early Experiences Developing and Debugging on the Intel® Xeon Phi Coprocessor       | 401/402/403            |

| 5:30-7:00  | Birds of a Feather      | Eclipse Parallel Tools Platform (PTP)                                               | 210/212                |

| 5:30-7:00  | Birds of a Feather      | Energy Efficient High Performance Computing                                         | 205/207                |

| 5:30-7:00  | Birds of a Feather      | G8 Extreme Scale and Big Data Program: Progress on Current Exascale Projects        | 501/502                |

| 5:30-7:00  | Birds of a Feather      | HPC and the Web                                                                     | 703                    |

| 5:30-7:00  | Birds of a Feather      | Library of Mini-Applications for Exascale Component-Based Performance Modelling     | 708/710/712            |

| 5:30-7:00  | Birds of a Feather      | MPICH: A High-Performance Open-Source MPI Implementation                            | 201/203                |

| 5:30-7:00  | Birds of a Feather      | OpenMP Goes Heterogeneous With OpenMP 4.0                                           | 301/302/303            |

|            |                         |                                                                                     |                        |

# **Tuesday, November 19** (Continued)

| Time      | Event              | Session                                                        | Location        |

|-----------|--------------------|----------------------------------------------------------------|-----------------|

| 5:30-7:00 | Birds of a Feather | Science and Scientific Workflows: Putting Workflows to Work    | 404             |

| 5:30-7:00 | Birds of a Feather | SUPReMM: Comprehensive Open Source Resource Management         | 507             |

| 5:30-7:00 | Birds of a Feather | TOP500 Supercomputers                                          | Mile High       |

| 5:30-7:00 | Birds of a Feather | Towards Exascale Runtime Systems: Challenges and Opportunities | 503/504         |

| 5:30-7:00 | Birds of a Feather | Trends in Small HPC Center Management                          | 705/707/709/711 |

# Wednesday, November 20

| Time       | Event                       | Session                                                                    | Location               |

|------------|-----------------------------|----------------------------------------------------------------------------|------------------------|

| 8:30-10:00 | Invited Talks               | Invited Talks (4)                                                          | Mile High              |

| 8:30-5:00  | Posters                     | ACM Student Research Competition Poster Exhibit                            | Mile High Pre-Function |

| 8:30-5:00  | Posters                     | Research Poster Exhibit                                                    | Mile High Pre-Function |

| 8:30-5:00  | Scientific Viz Showcase     | Exhibit                                                                    | Mile High Pre-Function |

| 10:00-5:30 | Emerging Technologies       | Emerging Technologies                                                      | Booth 3547             |

| 10:00-3:00 | HPC Interconnections        | Student Job/Opportunity Fair                                               | 605/607                |

| 10:00-4:30 | Student Cluster Competition | Student Cluster Competition                                                | Booth 3146             |

| 10:20-2:30 | HPC Impact Showcase         | Showcase Wednesday                                                         | Booth 3947             |

| 10:30-Noon | Awards                      | ACM Gordon Bell Finalists II                                               | 201/203                |

| 10:30-Noon | Panel                       | Large Supercomputers and Networks (International Panel)                    | 301/302/303            |

| 10:30-Noon | Papers                      | Optimizing Data Movement                                                   | 205/207                |

| 10:30-Noon | Papers                      | Parallel Programming Models and Compilation                                | 405/406/407            |

| 10:30-Noon | Papers                      | Performance Management of HPC Systems                                      | 401/402/403            |

| 10:30-Noon | Exhibitor Forum             | Effective Application of HPC I                                             | 503/504                |

| 10:30-Noon | Exhibitor Forum             | HPC Futures & Exascale I                                                   | 501/502                |

| 10:30-Noon | HPC Educators               | An Educator's Toolbox for CUDA (Part 1)                                    | 708/710/712            |

| 10:30-Noon | HPC Educators               | Unveiling parallelization strategies at undergraduate level                | 702/704/706            |

| 10:30-Noon | HPC Undergraduate           | Graduate Student Perspective                                               | 703                    |

| 10:30-Noon | Invited Talks               | Invited Talks (5)                                                          | Mile High              |

| 12:15-1:15 | Birds of a Feather          | Application Migration and Performance Expectation for Manycore Programming | 205/207                |

| 12:15-1:15 | Birds of a Feather          | Applications of LLVM to HPC                                                | 201/203                |

| 12:15-1:15 | Birds of a Feather          | At the Intersection of Big Data and Extreme Computing                      | 503/504                |

| 12:15-1:15 | Birds of a Feather          | Chapel Lightning Talks 2013                                                | 601/603                |

| 12:15-1:15 | Birds of a Feather          | Community MOOC's for Computing Technologies and Applications               | 705/707/709/711        |

| 12:15-1:15 | Birds of a Feather          | Heterogeneous Computing Platforms: Merging HPC and Embedded                | 708/710/712            |

| 12:15-1:15 | Birds of a Feather          | High Precision Arithmetic Operations: Libraries and Applications           | 301/302/303            |

| 12:15-1:15 | Birds of a Feather          | High-Performance Communications for High-Performance Computing             | 404                    |

| 12:15-1:15 | Birds of a Feather          | HPC Job Scheduling Challenges and Successes from the PBS Community         | 702/704/706            |

| 12:15-1:15 | Birds of a Feather          | HPC Systems Engineering and Administration                                 | 501/502                |

| 12:15-1:15 | Birds of a Feather          | INCITE and Leadership-Class Systems                                        | 703                    |

| 12:15-1:15 | Birds of a Feather          | Opportunities and Barriers for Computational Science Education             | 507                    |

| 12:15-1:15 | Birds of a Feather          | PGAS: The Partitioned Global Address Space Programming Model               | 401/402/403            |

|            |                             |                                                                            |                        |

# Wednesday, November 20 (Continued)

|            |                             | (                                                                             |                 |

|------------|-----------------------------|-------------------------------------------------------------------------------|-----------------|

| Time       | Event                       | Session                                                                       | Location        |

| 12:15-1:15 | Birds of a Feather          | The Open Community Runtime (OCR) Framework for Exascale Systems               | 405/406/407     |

| 12:15-1:15 | Birds of a Feather          | Total Power Usage Effectiveness: A New Take on PUE                            | 210/212         |

| 1:30-3:00  | Panel                       | RDMA: Scaling the I/O Architecture for Future Applications                    | 301/302/303     |

| 1:30-3:00  | Papers                      | Fault-Tolerant Computing                                                      | 201/203         |

| 1:30-3:00  | Papers                      | In-Situ Data Analytics and Reduction                                          | 205/207         |

| 1:30-3:00  | Papers                      | Parallel Performance Tools                                                    | 405/406/407     |

| 1:30-3:00  | Papers                      | Preconditioners and Unstructured Meshes                                       | 401/402/403     |

| 1:30-3:00  | Exhibitor Forum             | Effective Application of HPC II                                               | 503/504         |

| 1:30-3:00  | Exhibitor Forum             | HPC Futures & Exascale II                                                     | 501/502         |

| 1:30-3:00  | HPC Educators               | An Educator's Toolbox for CUDA (Part 2)                                       | 708/710/712     |

| 1:30-3:00  | Invited Talks               | Invited Talks (6)                                                             | Mile High       |

| 1:30-3:00  | Student Cluster Competition | Get Involved in the Student Cluster Competition                               | 703             |

| 1:30-5:00  | HPC Educators               | CSinParallel: Using Map-Reduce to Teach Data-Intensive Scalable Computing     | 702/704/706     |

| 3:30-5:00  | Posters                     | ACM Student Research Competition Poster Presentations                         | 404             |

| 3:30-5:00  | Broader Engagement          | Session VI: Journal Publishing 101                                            | 703             |

| 3:30-5:00  | Exhibitor Forum             | HPC Futures & Exascale III                                                    | 501/502         |

| 3:30-5:00  | HPC Educators               | An Educator's Toolbox for CUDA (Part 3)                                       | 708/710/712     |

| 3:30-5:00  | Invited Talks               | Invited Talks (7)                                                             | Mile High       |

| 3:30-5:00  | Panel                       | Fault Tolerance/Resilience at Petascale/Exascale: Is it Really Critical?      | 301/302/303     |

| 3:30-5:00  | Papers                      | Engineering Scalable Applications                                             | 401/402/403     |

| 3:30-5:00  | Papers                      | Improving Large-Scale Computation and Data Resources                          | 205/207         |

| 3:30-5:00  | Papers                      | Tools for Scalable Analysis                                                   | 405/406/407     |

| 4:30-5:30  | Student Cluster Competition | Grand Finale                                                                  | Booth 3146      |

| 5:30-6:00  | Student Cluster Competition | "Celebrity Pro-Am Cluster Challenge" Kickoff                                  | Booth 3146      |

| 5:30-7:00  | Birds of a Feather          | Big Data, Big Compute: Data-Intensive and Extreme-Scale Computing             | 301/302/303     |

| 5:30-7:00  | Birds of a Feather          | Codesign for the Department of Energy's Computational Science Community       | 702/704/706     |

| 5:30-7:00  | Birds of a Feather          | Cost-Benefit Quantification for HPC: An Inevitable Challenge                  | 601/603         |

| 5:30-7:00  | Birds of a Feather          | Creating a Training Roadmap for New Computational Consultants and Their Users | 703             |

| 5:30-7:00  | Birds of a Feather          | Critically Missing Pieces in Heterogeneous Accelerator Computing              | 401/402/403     |

| 5:30-7:00  | Birds of a Feather          | Drilling Down: Understanding User-Level Activity on Today's Supercomputers    | 205/207         |

| 5:30-7:00  | Birds of a Feather          | Evolution of and Experiences with OpenACC                                     | 705/707/709/711 |

| 5:30-7:00  | Birds of a Feather          | Exascale IO Initiative: Progress Status                                       | 708/710/712     |

| 5:30-7:00  | Birds of a Feather          | OpenCL: Version 2.0 and Beyond                                                | 405/406/407     |

| 5:30-7:00  | Birds of a Feather          | OpenSHMEM: Further Developing a Standard for the PGAS & SHMEM Community       | 201/203         |

| 5:30-7:00  | Birds of a Feather          | Reconfigurable Supercomputing                                                 | 503/504         |

| 5:30-7:00  | Birds of a Feather          | Research Data Alliance (RDA) for HPC                                          | 501/502         |

| 5:30-7:00  | Birds of a Feather          | Super-R: Supercomputing and R for Data-Intensive Analysis                     | 404             |

| 5:30-7:00  | Birds of a Feather          | Techniques and Strategies for Extreme Scale Debugging                         | 210/212         |

| 5:30-7:00  | Birds of a Feather          | The Green500 List and Its Evolution                                           | Mile High       |

|            |                             |                                                                               |                 |

# Wednesday, November 20 (Continued)

| Time       | Event                       | Session                       | Location   |

|------------|-----------------------------|-------------------------------|------------|

| 5:30-7:00  | Birds of a Feather          | Women in HPC Around the World | 507        |

| 6:00-10:00 | Student Cluster Competition | Dinner                        | Booth 3146 |

# Thursday, November 21

| maisa         | ay, Hovelinger Ex           |                                                                                       |                        |

|---------------|-----------------------------|---------------------------------------------------------------------------------------|------------------------|

| Time          | Event                       | Session                                                                               | Location               |

| 7:30-8:30     | HPC Undergraduate           | Experiencing HPC For Undergraduates Breakfast                                         | 703                    |

| 8:30-10:00    | Invited Talks               | Invited Talks (8)                                                                     | Mile High              |

| 8:30-Noon     | Scientific Viz Showcase     | Exhibit                                                                               | Mile High Pre-Function |

| 8:30-5:00     | Posters                     | ACM Student Research Competition Poster Exhibit                                       | Mile High Pre-Function |

| 8:30-5:00     | Posters                     | Research Poster Exhibit                                                               | Mile High Pre-Function |

| 10:00-14:00   | Emerging Technologies       | Emerging Technologies                                                                 | Booth 3547             |

| 10:00-11:30   | Student Cluster Competition | "Celebrity Pro-Am Cluster Challenge"                                                  | Booth 3146             |

| 10:20-1:00    | HPC Impact Showcase         | Showcase Thursday                                                                     | Booth 3947             |

| 10:30-Noon    | Panel                       | Emerging Technologies and Big Data (Euro-Centric)                                     | 301/302/303            |

| 10:30-Noon    | Papers                      | GPU Programming                                                                       | 205/207                |

| 10:30-Noon    | Papers                      | Matrix Computations                                                                   | 401/402/403            |

| 10:30-Noon    | Papers                      | Memory Resilience                                                                     | 405/406/407            |

| 10:30-Noon    | Papers                      | Performance Analysis of Applications at Large Scale                                   | 201/203                |

| 10:30-Noon    | Doctoral Showcase           | Dissertation Research                                                                 | 601/603                |

| 10:30-Noon    | Exhibitor Forum             | Moving, Managing & Storing Data III                                                   | 503/504                |

| 10:30-Noon    | Exhibitor Forum             | Software for HPC I                                                                    | 501/502                |

| 10:30-Noon    | HPC Undergraduate           | Careers in HPC                                                                        | 703                    |

| 10:30-Noon    | Invited Talks               | Invited Talks (9)                                                                     | Mile High              |

| 10:30-Noon    | Network Research Exhibition | Network Research Exhibition                                                           | 404                    |

| 10:30-12/1:30 | -3:00 HPC Educators         | Going Parallel with C++11 (Parts 1 &2)                                                | 702/704/706            |

| 12:15-1:15    | Birds of a Feather          | Application Grand Challenges in the Heterogeneous Accelerator Era                     | 401/402/403            |

| 12:15-1:15    | Birds of a Feather          | Computer Architecture Repositories for Open Simulation and Modeling Tools             | 404                    |

| 12:15-1:15    | Birds of a Feather          | Coprocessors, GPUs, MICs: Enticing Users to Jump onto Accelerators                    | 405/406/407            |

| 12:15-1:15    | Birds of a Feather          | Discussing an I/O Framework to Accelerate Improvements in Application I/O Performance | 601/603                |

| 12:15-1:15    | Birds of a Feather          | Ethernet's Rate Roadmap                                                               | 702/704/706            |

| 12:15-1:15    | Birds of a Feather          | Harnessing Accelerator Technology for Next-Gen Sequencing Bioinformatics              | 503/504                |

| 12:15-1:15    | Birds of a Feather          | HPC Training Perspectives and Collaborations from PRACE, XSEDE and RIKEN AICS         | 501/502                |

| 12:15-1:15    | Birds of a Feather          | New Developments in the APGAS Programming Model and X10                               | 507                    |

| 12:15-1:15    | Birds of a Feather          | Petascale Systems with Intel Xeon Phi Co-Processors                                   | 301/302/303            |

| 12:15-1:15    | Birds of a Feather          | Slurm User Group Meeting                                                              | 205/207                |

| 12:15-1:15    | Birds of a Feather          | The 2013 HPC Challenge Awards                                                         | 201/203                |

| 12:15-1:15    | Birds of a Feather          | The Message Passing Interface: Version 3.0 and What Comes Next?                       | 705/707/709/711        |

| 12:15-1:15    | Birds of a Feather          | The UDT Forum: A Community for UDT Developers and Users                               | 703                    |

| 12:30-1:30    | Awards                      | SC13 Conference Awards Presentations                                                  | Mile High              |

| 1:30-3:00     | Awards                      | ACM Athena Award / SC13 Test of Time Award Special Lectures                           | Mile High              |

|               |                             |                                                                                       |                        |

# Thursday, November 21 (Continued)

| Time       | Event                       | Session                                                               | Location          |

|------------|-----------------------------|-----------------------------------------------------------------------|-------------------|

| 1:30-3:00  | Doctoral Showcase           | Dissertation Research                                                 | 601/603           |

| 1:30-3:00  | Exhibitor Forum             | Moving, Managing & Storing Data IV                                    | 503/504           |

| 1:30-3:00  | Exhibitor Forum             | Software for HPC II                                                   | 501/502           |

| 1:30-3:00  | Network Research Exhibition | Network Research Exhibition                                           | 404               |

| 1:30-3:00  | Panel                       | Extreme Computing and Industrial Competitiveness                      | 301/302/303       |

| 1:30-3:00  | Papers                      | Memory Hierarchy                                                      | 405/406/407       |

| 1:30-3:00  | Papers                      | MPI Performance and Debugging                                         | 201/203           |

| 1:30-3:00  | Papers                      | Sorting and Graph Algorithms                                          | 205/207           |

| 3:00-5:00  | Broader Engagement          | Wrap Up/Scavenger Hunt Awards                                         | 705/707/709/711   |

| 3:30-5:00  | Doctoral Showcase           | Early Research Showcase                                               | 601/603           |

| 3:30-5:00  | Exhibitor Forum             | Moving, Managing & Storing Data V                                     | 503/504           |

| 3:30-5:00  | Exhibitor Forum             | Software for HPC III                                                  | 501/502           |

| 3:30-5:00  | HPC Educators               | High-level parallel programming using Chapel (Part 2)                 | 708/710/712       |